Overview of Digital design methodology, Representations of Digital Design and understanding of digital systems, logic gates, combinational and sequential logic. Review HDL’s and RTL implementation of digital logic systems.

Introduction to semiconductor technologies, logic gates, Review CMOS basics, CMOS digital design concepts. Understanding CMOS process parameters and characterization of logic gates

Overview of ASIC/SOC design flow, Digital Design Concepts and Introduction to design faults that occur during chip design. Understanding stuck at faults, transition faults, coupling faults, pattern sensitive faults, and dynamic faults.

a) DFT fundamentals

b) Need for DFT in chip design

c) Understanding fabrication flows and challenges

d) ATPG basics

a) Observability and Controllability

b) DFT Scan logic design

c) DFT Design rules

d) Scan register vs normal registers

e) Scan chains & Scan pipelines

f) Scan Insertion techniques

g) Scan protocol design

a) DFT flows and process steps

b) Defining DFT scan constraints

c) DFT synthesis and review scan protocols

d) DRC Checks (DFT Rule Checks)

e) DRC Error reporting and categories

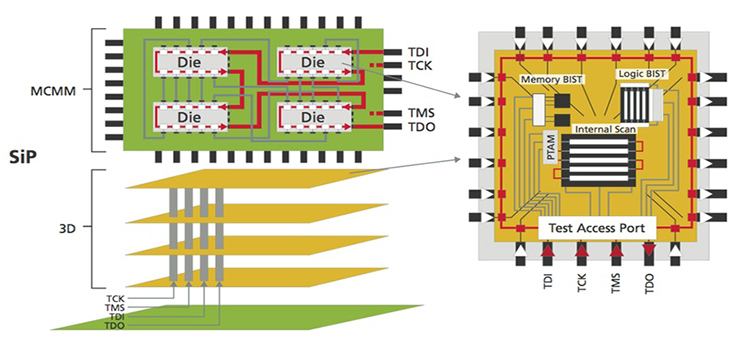

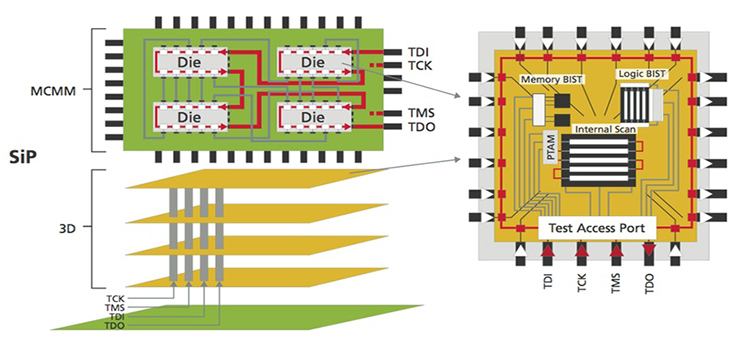

f) Over view of block level & SoC level DFT scan design

a) Scan Chain Architecture

b) Mux-D Scan Design

c) Clocked Scan Design

d) Level Sensitive Scan Design(LSSD)

e) Enhanced Scan Design

f) Low-Power Scan Design

a) BIST Controllers

b) BIST Test Pattern Generators

c) Test pattern compaction

d) BIST Architectures

e) Test Per Scan BIST

f) Test Per Clock BIST

g) STUMPS based BIST Architecture

h) CBILBO BIST Architecture

i) Coverage Driven Logic BIST

j) Low Power BIST

a) Scan Synthesis flows

b) DFT tools and setup for scan insertion

c) Scan Constraints and protocol definitions

d) Setting ATE configuration

e) Scan Specifications

f) Pre and Post Scan checks

g) Identifying Scan Chains and Estimating Test Coverages

h) Scan DRC(DFT rule checker) checks

i) Scan Chain optimization

a) Scan Issues with various design scenarious

b) Gated clocks and clock muxes, Clock Generators

c) Controllability of Asynchronous logic, resets

d) Scan Design initialization sequence

e) Scan Capture problems due to clock skews

f) Scan buffers, Shift registers, tristate & bidirectional ports

g) Latch based designs and combinational loops

a) Scan chain insertion with Clock mixing and no mixing

b) Mixing clock edges, clocking on both edges

c) Internal clock domains

d) Lockup latch

e) Custom Scan paths

f) Scan in/out port sharing techniques

a) DFT Scan compression with limited scan pins

b) Scan Serializer and Deserializer

c) Block level and Chip level compression techniques

d) External and Internal clock usage for serializer and Deserializer clocks

e) Adaptive scan techniques

a) BIST Architecture

b) Logic BIST

c) Memory BIST

d) RAM BIST

e) ROM BIST

f) Memory models

g) Memory Faults

h) Stuck open and short faults

i) Coupling faults

j) Pattern sensitive faults

k) Read Disturb faults

l) Dynamic faults, recovery faults retention faults

m) March Tests

n) Word oriented march tests

o) Inter and Intra word tests

p) Word coupling faults tests

q) MISR

a) Design Tools

b) ATPG tools and setup

c) ATE tools

d) STIL patterns( Defines Test protocols, Test pattern and Test timing )

e) Build Mode, DRC Mode and Test Mode

a) ATPG pattern generation constraints

b) Analyzing DFT rule violations

c) ATPG coverage estimation

d) ATPG STIL pattern generation

e) Dynamic and Static Pattern compression techniques

f) Review results Detectable and undetectable faults

a) Fault Simulation with functional patterns

b) Fault Grading for functional simulations

c) Design Verification setup with ATPG fault model simulations

d) Memory modeling for ATPG simulations

Project on Block level and SoC level DFT insertion and ATPG generation with fault model simulations

Trainer’s Name

Kishore NCourse Fee

:Available Seats

:Schedule

Regular & Weekend Batches

Sateesh N

Best DFT course structure and teaching faculty is excellent, provided complete guidance throught out the courses and projects.