a) Advanced Verilog Concepts.

b) Constant Functions.

c) Enhanced Operators.

d) Re-entrant tasks and Recursive Functions.

e) FILE I/O.

f) Common Compiler Directives.

g) Enhanced condition compilation.

h) Attributes.

i) Enhanced Invocation Option Tests.

j) New Timing Constraint Checks.

k) Verilog Configurations.

l) Verilog Generate.

m) Verilog PLI.

n) HVL Based verification.

a) Linting Tools.

b) Simulators.

c) Waveform Viewers.

d) Source Debugging Tools.

e) Code Coverage Tools.

f) Functional/Assertion Coverage Tools.

a) Functional Verification Process.

b) Test Plan Development.

c) TestBench Development

d) Testcase Development.

e) Behavioral Models Development.

f) BFM's Developments.

g) Monitors Development.

h) Checker Development.

i) Functional group & Assert group Development using OVL & SVA.

j) Module/Block/Chip Level Verification.

k) Coverage driven Random Verification.

l) Verification Metric Analysis (Code & Function coverage analysis)

a) Zero-Delay Gate-Level Verification.

b) SDF-Annotated Gate-Level Verification.

c) Timing Verification Process.

d) Introduction to Formal Verification.

e) Introduction Power-Aware Verification.

f) Introduction to co-simulation verification.

g) Introduction to AMS Verification.

h) Introduction to Physical Verification

a) Introduction to Scripting using Perl.

b) Linux/Unix Utilities.

c) FTP.

d) Telnet.

e) Version Management.

f) Bug Tracking.

a) Language evolution

b) SV Design

c) SV Assertions

d) SV testbench

e) DPI

f) API

a) Data types, type checking, type cast

b) Structure and union

c) Packages

d) Enhanced always, case/if... else, loop, flow

e) Operators

f) Arrays and its operators SV scheduling semantics

g) DUT description

h) Interface

i) Grouping signals

j) Modport

k) Clocking block, skews

l) Tasks, functions

m) Transaction Level Modeling (TLM)

a) Object Oriented programming (OOP's)

b) Type cast

c) inheritance

d) polymorphism

e) parameterization

f) new constructor

g) Automatic garbage collection

h) Virtual interface

i) task and function

j) automatic and static functions (void & extern)

k) Argument pass by value/reference

l) Program construct

m) Final block

n) Enhanced Concurrency modeling

o) Threads – variants of fork .. join, Disable fork, terminate

a) Events

b) semaphore

c) mailboxes

d) queues

a) Need for random testing

b) Constraints in SVTB

c) Class constraint

d) Randomize success / fail

e) Inheritance Randomize.with()

f) Distribution

g) Function calls in constraints

h) Array constraints

i) Pre / post randomize

a) Motivation for SV Coverage Driven verification

b) Introduction to SV coverage

c) Types of coverage

d) Functional coverage process Covergroup

e) Coverpoint

f) Concept of binning

g) Cross Coverage

h) Sampling event

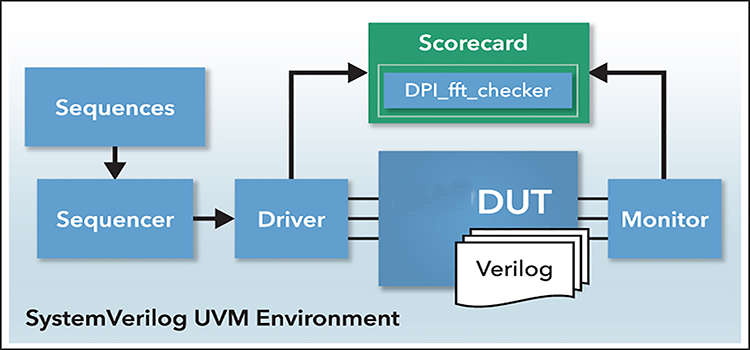

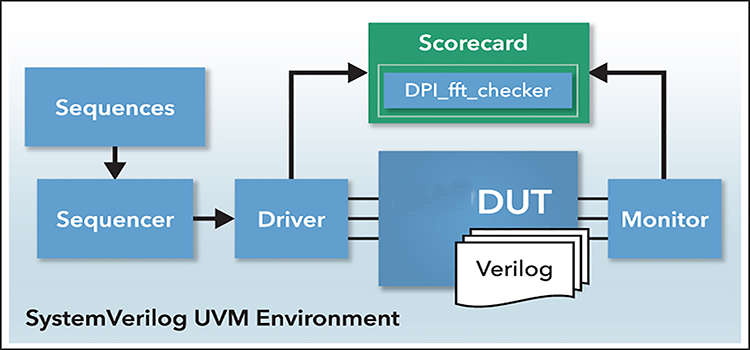

a) Import DPI

b) Export DPI

c) DPI Context

d) DPI vs. VPI/PLI

a) Overview of different verification methodologies

b) Evolution of Verification methodologies

c) Migration of OVM to UVM

d) Introduction to UVM

e) Verification phasing

f) Reporting

g) Transactions

h) Test bench Configuration

i) TLM Basics

j) Events, Sequence, Sequencer and Driver Virtual Sequences

k) Monitor & Subscriber

l) Agents

m) UVM Environment

n) Test bench classes

o) Callbacks

p) Coverage

q) Register layer

a) AHB Master/slave

b) AXI Master/Slave

c) AHB-I2C

d) AHB Uart

e) AHB Memory controller.

f) Microcontrollers/DSP processors

g) DDR2

h) Ethernet

i) AXI Master/Slave

a) Zero Delay Simulations

B Power aware simulations

a) Functional Coverage

b) Code Coverage

Trainer’s Name

P SateeshCourse Fee

:Available Seats

:30Schedule

Regular & Weekend Batches

Best faculty to learn verification topics, thanks to Neoschip for providing this oppurtunty

I have taken verification training, theoritical sessions are very helpfull

Lakshmi Kiran

Teaching faculty is very helpfull and concepts are taught from basic level.